# **Development of Two High-Energy Bus 'Cores'** FOR RAPID SUPPORT OF LOW-TRL AND EDUCATIONAL PAYLOADS

# **NOW** The Nano Orbital Workshop

Rapid Flight Development Group

AMES RESEARCH CENTER

## Avery Brock, EE

The TechEdSat NOW Team:

Marcus Murbach PI, Seth Schisler PM, A. Salas, S. Krzesniak, M. Mooney-Rivkin, T. Stone, J. Alvarellos, S. Zuniga, K. Boateng, A. Rehman, T. Hector

# OUTLINE

TechEdSat Heritage Design The Challenge of Flexibility Spacecraft CoreStack Concept

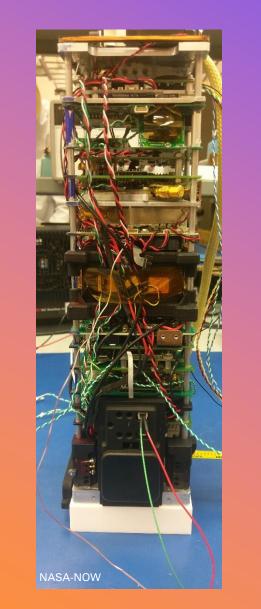

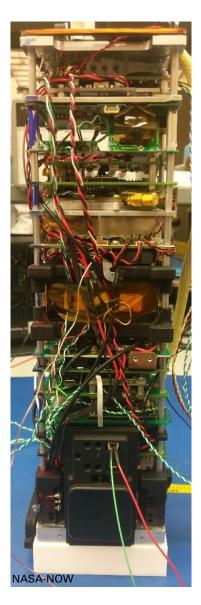

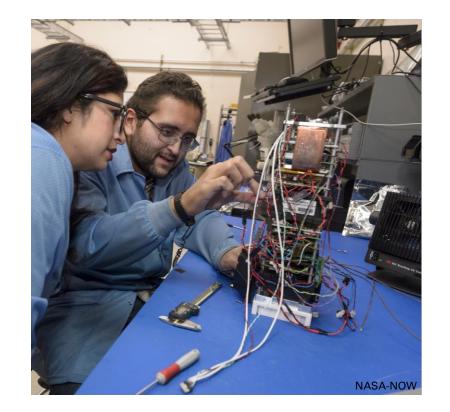

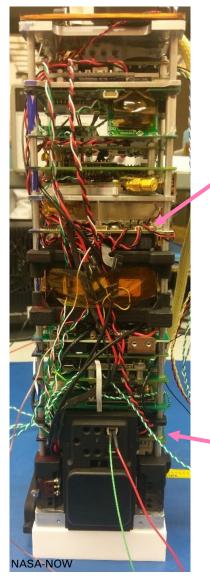

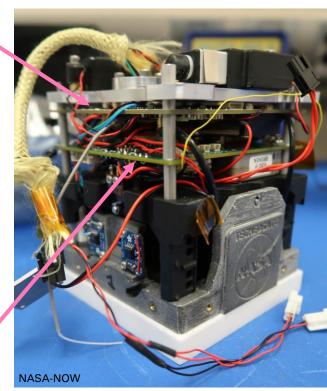

TechEdSat Stack Architecture:

- PC/104 perimeter PCBs, non-standard interconnects

- Discrete sub-systems are stacked and wired together

## **Benefits:**

- Very open standard provides extreme payload flexibility

- Makes design of and integration with structure easy

## **Drawbacks:**

- Hand-wiring of system is complex and time consuming

- Difficult to debug harnessing is sub-optimal

## Inhibiting:

TES Solar

TES Powerboard

uC

30 min delay

load contro

Load

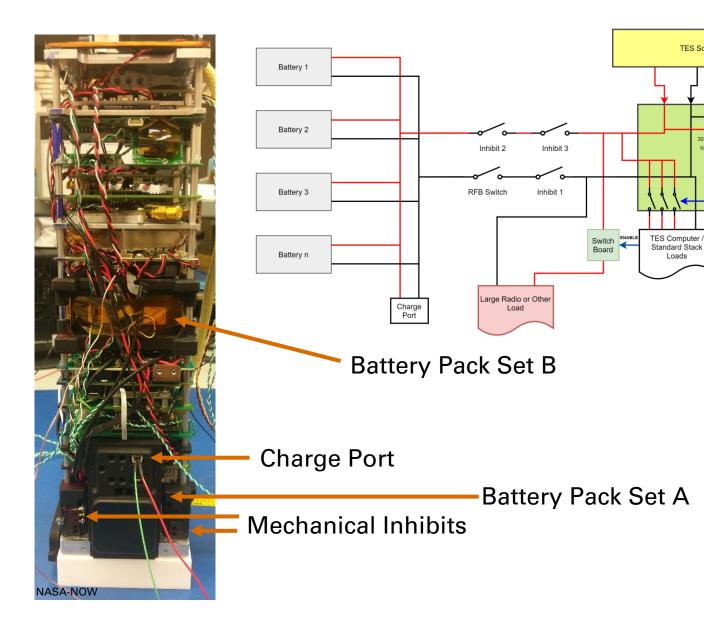

- ISS PSRP-approved inhibit scheme using triple-redundant mechanical switches

- 15-to-30-minute activation delay for ٠ radios, instant-on or software delay for payloads and other systems

#### **Power Management:**

- Direct connection of batteries to PDS and solar arrays (panel-based MPPT)

- **ISS-approved COTS camera batteries have** built-in protections and charge limiting

- Six-inch spacing requirement between 10Ah packs per ISS PSRP

Design has functioned for 20+ missions, but **TES** is outgrowing its power architecture

## 'Tardigrade' All-In-One Solution (Second-Gen)

#### 40-Watt All-In-One Board

- Vorago VA10820 processor

- 128KB flash, 32KB RAM

- 50 MHz ARM Cortex-M0 32

bit

- Rad-Hardened

- Six 2A solar panel channels

- Channel power monitoring

- Single battery channel

- Power monitoring

- External load buck or boost supplies and motor drivers

- Iridium 9603 and 2.4 GHz XBee3

- Mini GPS, Thermocouple channels, and a 3-axis Magnetometer

A single-board satellite design that was not pursued and fully developed; not quite the right fit

## 'Powerboard' Core C&DH and Power (First-Gen)

#### **14-Watt Power and Communication Board**

- ATmega328 processor obsolete

- 32KB flash, 2KB SRAM

- 16 MHz 8-bit processor

Half the memory of Apollo Guidance, yet running full missions with two bytes of free memory

- Four 3A solar panel channels

- Channel voltage monitoring

- Single battery channel

- Voltage and discharge current monitoring

- Power supply outputs to subsystems and driver for Exo-brake deployment

- Iridium 9602 modem

#### **TECHEDSAT 'CORES'**

6U TES-10

'Tardigrade' All-In-One Solution (Second-Gen)

'Powerboard' Core C&DH and Power (First-Gen)

2U TES-7

+

Combined C&DH and EPS/EPD single-board modules, i.e. Spacecraft 'Cores'

Powerboard has been the backbone of every TES mission, with Tardigrade recently supplementing

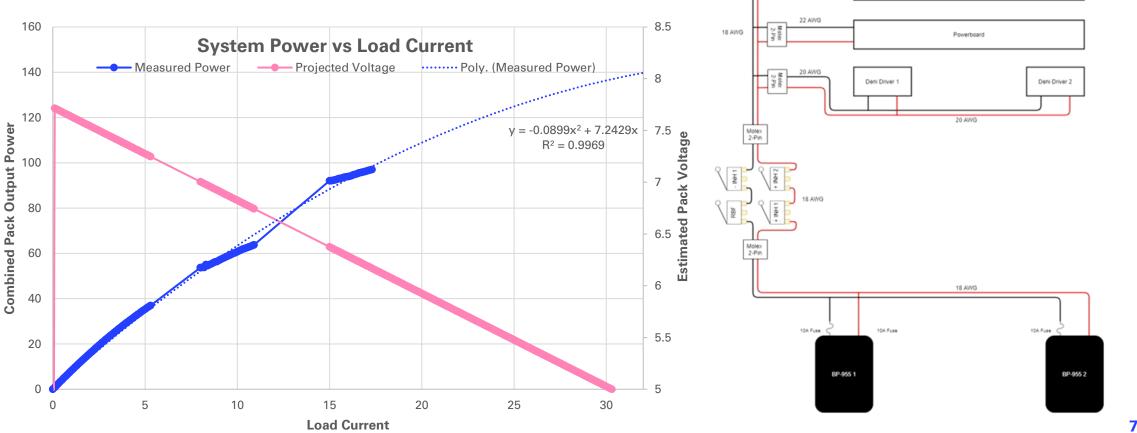

#### **CURRENT LIMITATIONS**

Lunar Radio

Tardigrade

18 AWG

22 AWG

Single low-voltage feed via mechanical inhibits inherently limits total system power due to resistive losses, regardless of Core design

Existing Cores cannot support a 50W payload

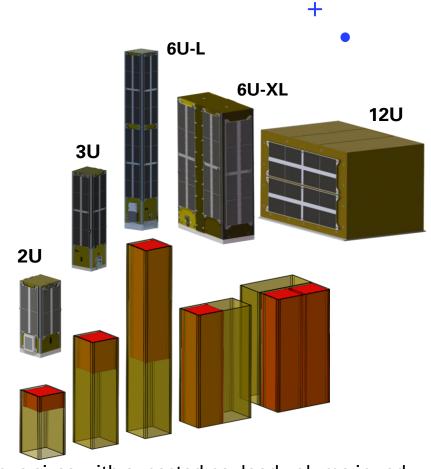

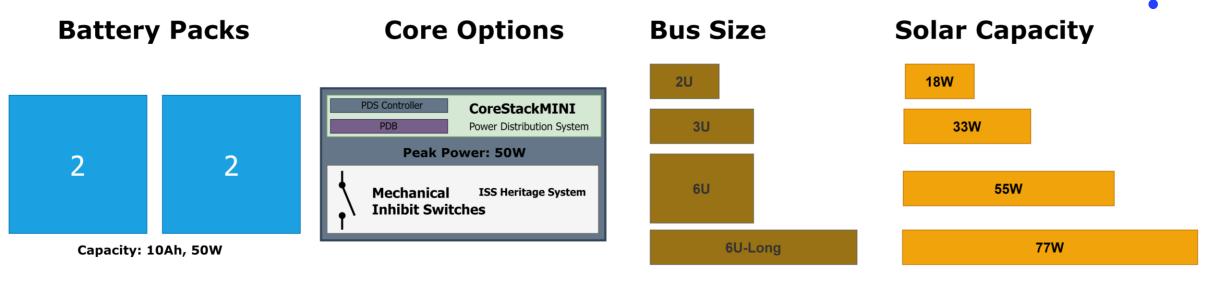

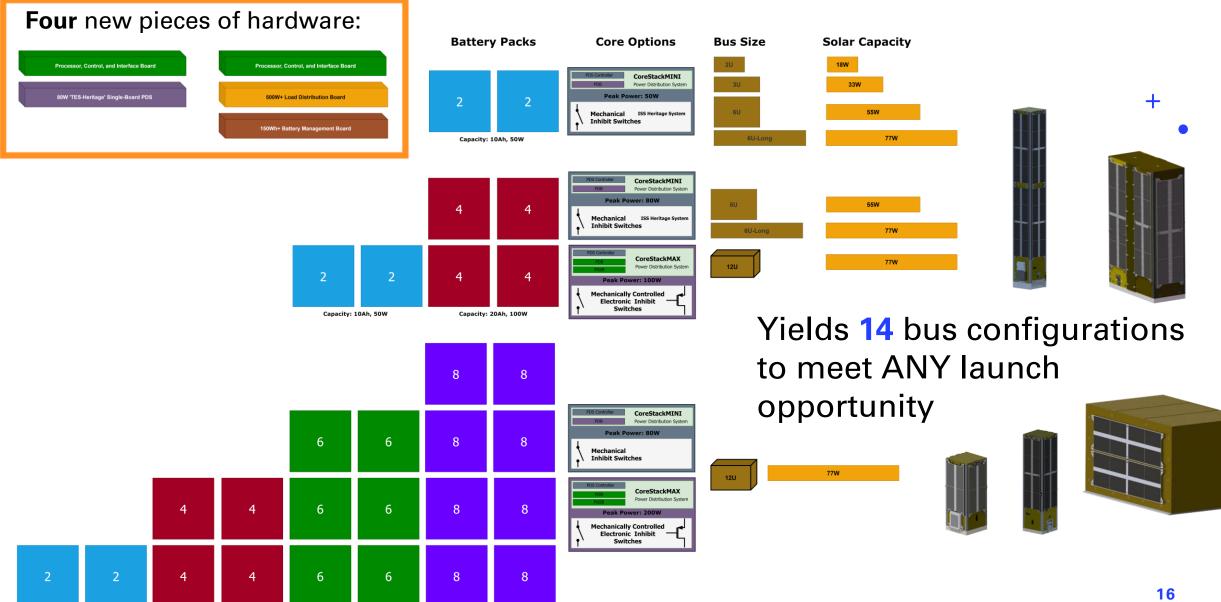

1. Support a multitude of bus sizes and power capabilities with a minimum of hardware:

- 0.5U, 1U, 3U, 6U-L, 6U-XL, & 12U+ Bus Sizes

- 10, 20, 30, & 40Ah+ battery pack configurations

- Balloon, sub-orbital, orbital, ISS, and beyond LEO mission desires

2. Support ISS PSRP heritage compliance while also supporting new space launchers and highenergy systems

3. Explicitly support third-party 'black-box' payloads, i.e., provide clean standardized interfaces unused by core avionics

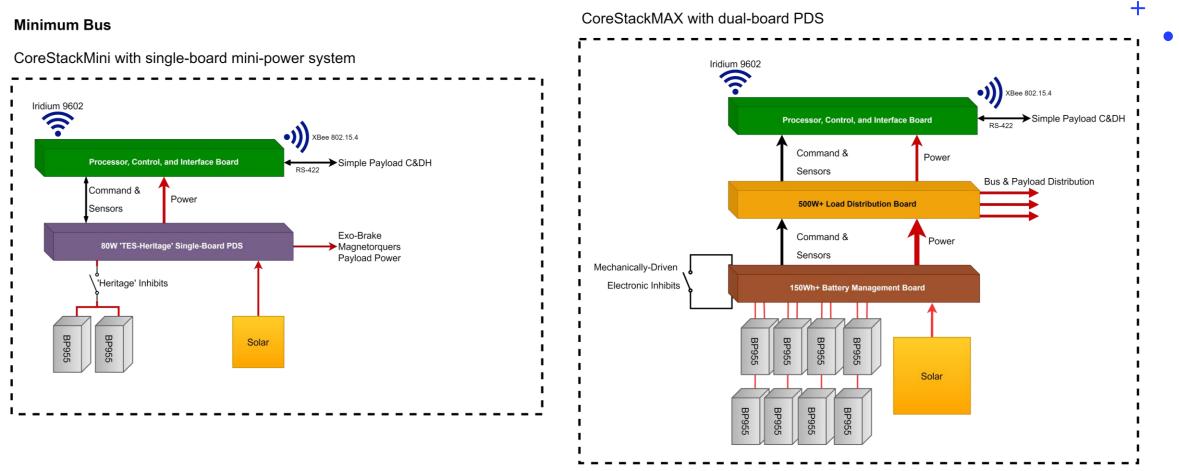

## TES 'Mini-Sat' Configuration: Minimum Bus 10Ah 50W Power Budget

50W ISS Heritage System – Direct Replacement

Solar Assumes TES SoA: 3.67 W/sqU, 3 sqU and endcaps uncovered

**CONFIGURATIONS**

## **TES 'Standard' Configuration**

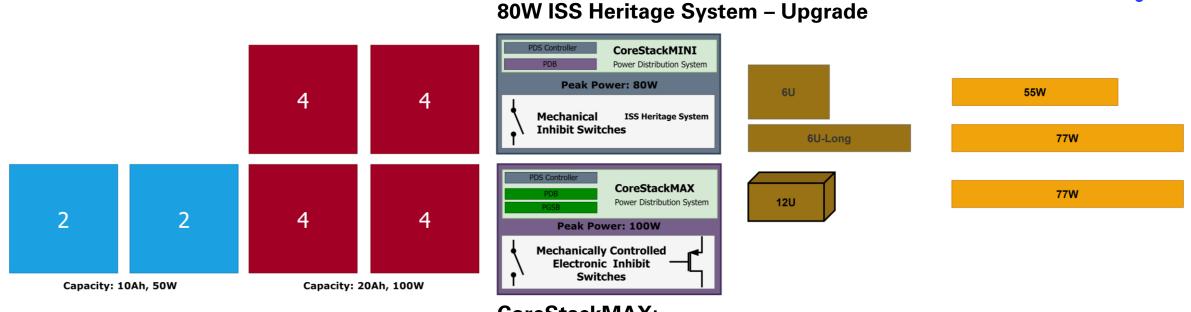

20Ah 80W ISS Power Budget 20Ah 100W New-Space Power Budget

**CoreStackMINI:**

CoreStackMAX: 100W System – Novel Hardware

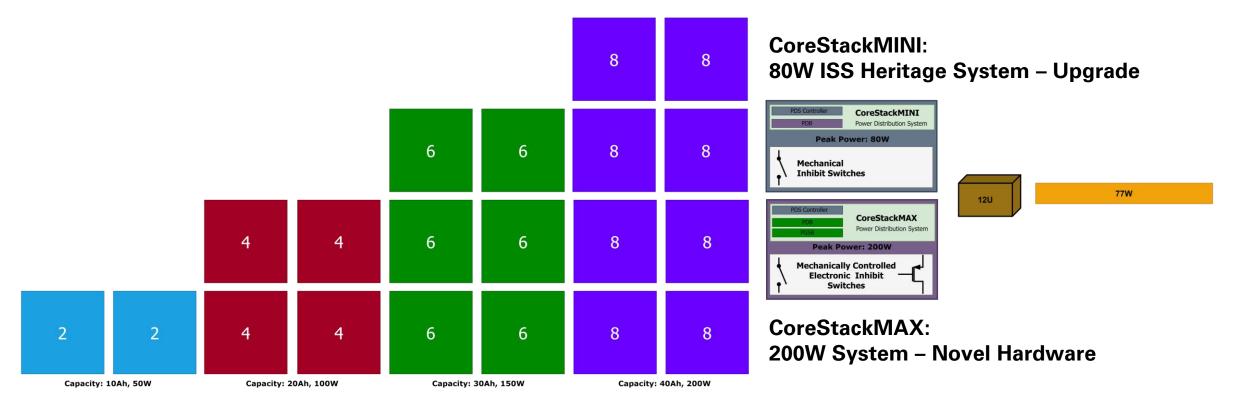

#### NANO ORBITAL WORKSHOP CONFIGURATIONS

## TES 12U Configurations Up to 40Ah 200W Power Budget on New-Space Launchers

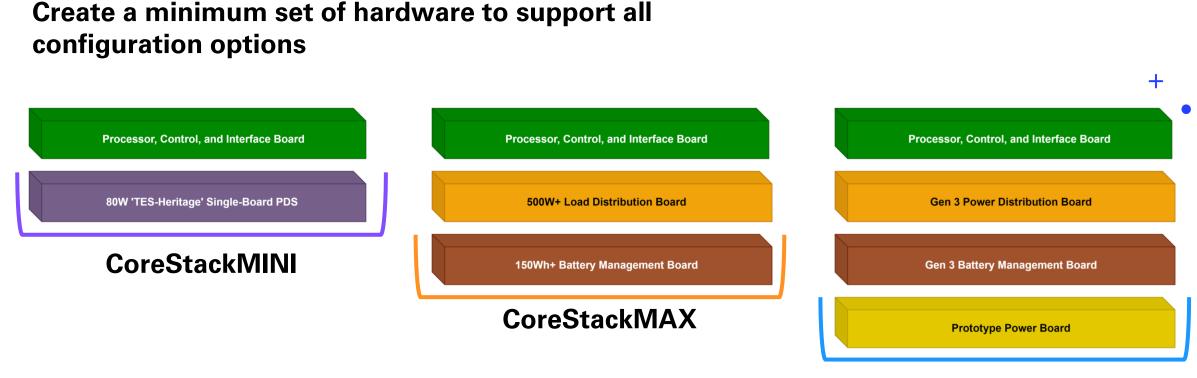

CORESTACK CONCEPT

**CoreStack-X**

One Controller board to standardize processor, code, and comms

Two sets of Power Distribution/Management boards designed to two broad power and inhibit schemes

## **Satellite Configurations:**

## Maximum Bus

CORESTACK DEVELOPMENT

### Controller

Complete the design and layout of new CoreStack controller; start software development

## Mini PDS

Complete the design of and build the new singleboard ISS-inhibit scheme 80W PDS and fly it

## Max PDS

Develop the twoboard 200W+ PDS stack and begin laboratory and environmental testing

## Optimize System

Begin optimizing other TES systems to better mesh with the new CoreStack system to ease integration

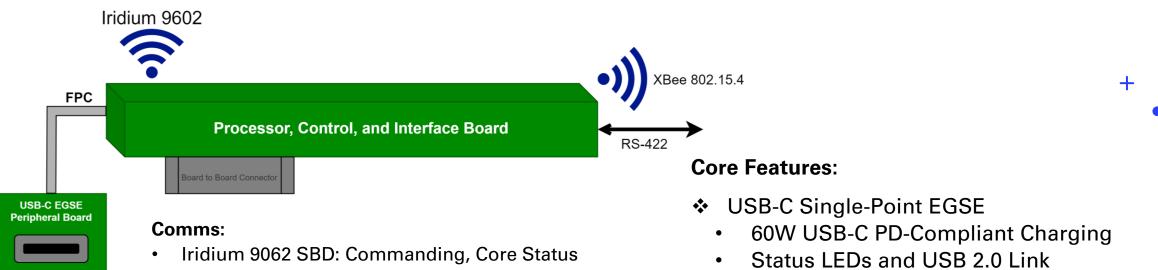

#### **CORESTACK CONTROLLER**

- XBee3 802.15.4: Inter-Spacecraft Mesh Network ٠

- RS-422 Hardline: Inter-Spacecraft Network

#### Memory:

- 8Mb Program FRAM Vorago MCU

- 4Mb Data/Configuration FRAM

#### Other:

- Flight-Heritage RTC

- **GPS Signal Feedthrough**

- Standardized Board to Board Interface

- Unconstrained serial interfaces, no GPIO limitations

- Multiple Processor Options \*\*

- Interoperable footprints for several microcontrollers

- Teensy 4.0, 3.2 TES Heritage

- Adafruit Feather SAMD21 ARM-M0, SAMD51 ARM-M4

- Embedded Vorago ARM-M4 Rad-hard

- Single-Board Blackbox ••••

- Total power system failure survival with sensor polling and final packets comms

Capacity: 10Ah, 50W

Capacity: 20Ah, 100W

Capacity: 30Ah, 150W

Capacity: 40Ah, 200W

# Development of Two High-Energy Bus 'Cores' FOR RAPID SUPPORT OF LOW-TRL AND EDUCATIONAL PAYLOADS